Khác với transistor lưỡng cực (BJT- Bipolar junction transistor) mà đặc điểm chủ yếu là dòng điện trong chúng do cả hai loại hạt dẫn (điện tử và lỗ trống) tạo nên (xem lại tại đây), transistor trường (Field Effect Transistor – FET) hoạt động dựa trên nguyên lý hiệu ứng trường, điều khiển độ dẫn điện của đơn tinh thể bán dẫn nhờ tác dụng của một điện trường ngoài. Dòng điện trong FET chỉ do một loại điện tích tạo nên.

Công nghệ bán dẫn, vi điện tử càng tiến bộ, FET càng tỏ rõ ưu điểm quan trọng trên mặt xử lý gia công tín hiệu với độ tin cậy cao và mức tiêu hao năng lượng cực bé.

Công nghệ bán dẫn, vi điện tử càng tiến bộ, FET càng tỏ rõ ưu điểm quan trọng trên mặt xử lý gia công tín hiệu với độ tin cậy cao và mức tiêu hao năng lượng cực bé.

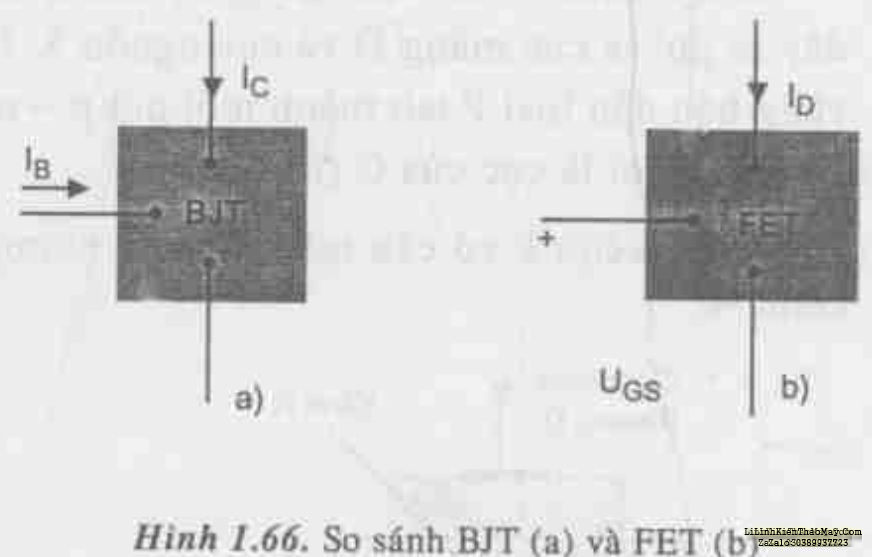

Sự khác nhau cơ bản giữa BJT và FET được chỉ rõ ở hình 1.66.

Transistor hiệu ứng trường FET gồm có hai loại chính:

FET điều khiển bằng tiếp xúc p – n (hay gọi là FET mối nối đơn): Junction FET, viết tắt là JFET. Chính là phần nội dung được đề cập phía dưới.

FET có cực cửa cách điện: Insulated Gate FET viết tắt là IGFET.

Thông thường lớp cách điện là lớp ôxít nên gọi là Metal Oxide Semiconductor FET (MOSFET hay MOS). Trong loại transistor trường có cực cửa cách điện lại chia làm hai loại là MOS có kênh sẵn và MOS có kênh cảm ứng. Xem thêm tại bài viết khác theo đường dẫn này.

Mỗi loại FET lại được chia làm hai loại, kênh N và kênh P.

Transistor trường có ba chân cực: cực nguồn (Source) ký hiệu là S, cực cổng (Gate) ký hiệu là G và cực máng ký hiệu là D (Drain).

– Cực nguồn S là nơi mà các hạt dẫn đa số đi vào kênh và tạo ra dòng điện nguồn Is.

– Cuc máng D là nơi các hạt dẫn đa số đi ra khỏi kênh.

– Cực cửa G là cực điều khiển dòng điện chạy qua kênh.

Transistor trường có những ưu điểm nổi bật so với transistor lưỡng cực BJT là dòng điện qua FET chỉ do một loại hạt dẫn đa số tạo nên, do vậy FET là linh kiện một loại hạt dẫn. FET có trở kháng vào rất cao, tiếng ồn trong FET ít hơn nhiều so với BJT. Nó không bù điện áp tại vùng ID =0 và do đó nó là phần tử ngắt điện, FET có độ ổn định về nhiệt cao và có tần số làm việc cao. Tuy nhiên nó có nhược điểm là hệ số khuếch đại thấp hơn nhiều so với BJT.

Cấu tạo và đặc tính của JFET

1. Cấu tạo và ký hiệu của JFET

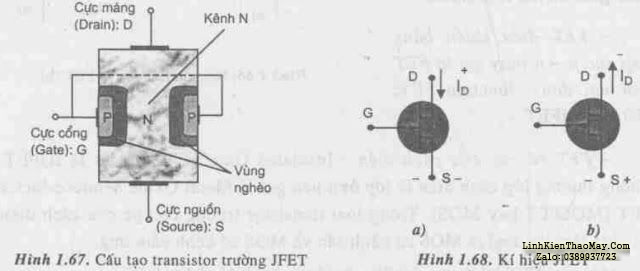

JFET được gọi là FET có mối nối đơn, có hai loại là JFET kênh N và kênh P.

JFET kênh N có cấu tạo gồm thanh bán dẫn loại N, hai đầu nối với hai dây ra gọi là cực máng D và cực nguồn S. Hai bên thanh bán dẫn loại N là hai vùng bán dẫn loại P tạo thành mối nối p- n như diode. Hai vùng này được nối với nhau gọi là cực cửa G (hình 1.67).

JFET kênh P có cấu tạo tương tự nhưng bóng bán dẫn ngược lại với JFET kênh N.

Ký hiệu của JFET như hình 1.68a (kênh N) và 1.68b (kênh P).

2. Đặc tính

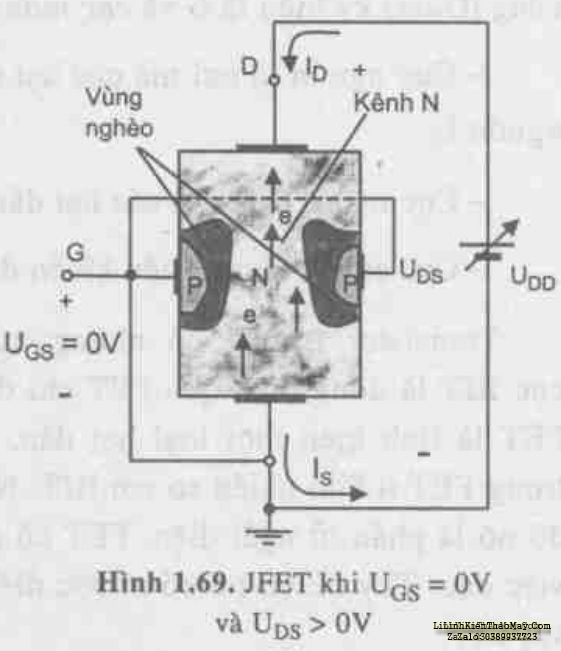

Xét JFET kênh N có cực D nối với dương nguồn, S nối với âm nguồn như hình 1.69.

Xét JFET kênh N có cực D nối với dương nguồn, S nối với âm nguồn như hình 1.69.

A. Khi cực G hở (UGS = 0V):

Lúc này dòng điện sẽ đi qua kênh theo chiều từ cực dương của nguồn vào cực D và ra ở cực S để trở về âm nguồn của UDD, kênh có tác dụng như một điện trở.

Nếu tăng điện thế UDS từ 0V lên thì dòng ID tăng lên nhanh nhưng sau đó đến một điện thế giới hạn thì dòng ID không tăng được nữa gọi là dòng điện bão hoà Idss. Điện thế UDS có IDSS goi là điện thế ngắt Up (pinch – off).

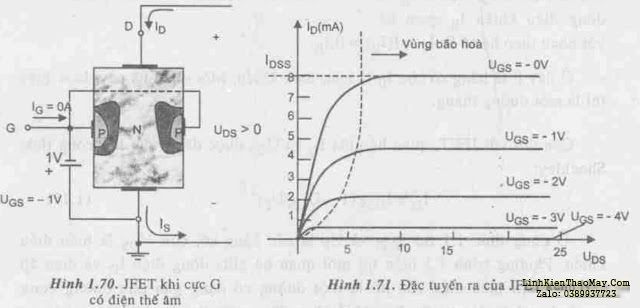

B. Khi cực G có điện thế âm (UGS<0V) hình 1.70

Khi cực G có điện thế âm nối vào bóng bán dẫn loại P, trong kênh N có dòng điện chạy qua nên có điện thế dương ở giữa bóng bán dẫn N sẽ làm cho mối nối P-N bị phân cực ngược làm điện tử trong bóng bán dẫn của kênh N bị đẩy và làm thu hẹp tiết diện kênh, nên điện trở kênh dẫn tăng lên, dòng ID giảm xuống.

Khi tăng điện thế âm ở cực G thì mức phân cực ngược càng lớn làm dòng ID càng giảm nhỏ và đến một giá trị giới hạn thì dòng ID gần như không còn. Điện thế này ở cực G gọi là điện thế ngắt Up.

Khi tăng điện thế âm ở cực G thì mức phân cực ngược càng lớn làm dòng ID càng giảm nhỏ và đến một giá trị giới hạn thì dòng ID gần như không còn. Điện thế này ở cực G gọi là điện thế ngắt Up.

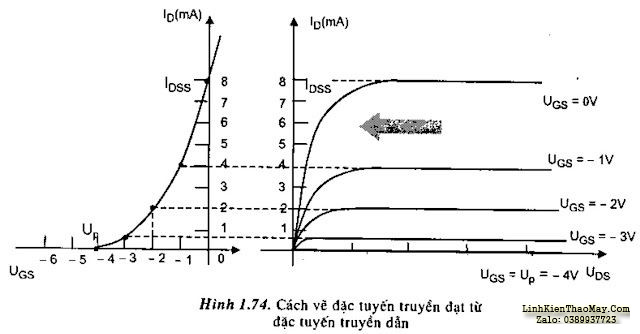

Hình 1.71 là đặc tuyển ra của JFET kênh N để chỉ sự thay đổi của ID theo UDS ứng với từng điện thế UGS ở cực G (gọi là họ đặc tuyến ID/UDS).

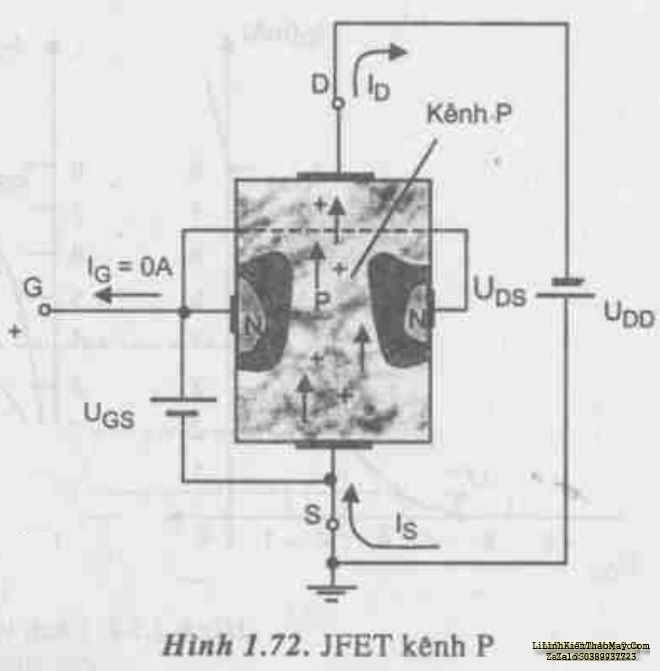

Đối với JFET kênh P: JFET kênh P có mạch thí nghiệm như hình 1.72 với nguồn UDD cung cấp cho UDS, điện thể cung cấp cho cực G bây giờ là điện thế dương (UG > US). JFET kênh P cũng có đặc tuyến ra giống như JFET kênh N nhưng có các dòng điện và điện thế ngược dấu.

3. Đặc tuyến truyền dẫn

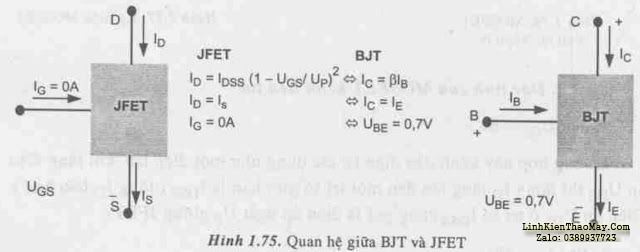

Đối với transistor lưỡng cực BJT thì dòng điện ra IC dòng điều khiển IB quan hệ với nhau theo hệ số β: IC = f(IB) = β.IB.

Ở đây β là hằng số còn IB là biến điều khiển. Mối quan hệ này được biểu thị là một đường thẳng.

Còn đối với JFET, quan hệ giữa ID và UGS được đặc trưng bởi công thức Shockley:

Ở công thức 1.17 thì IDSS và UP là các hằng số, còn UGS là biến điều khiển. Phương trình 1.17 biểu thị mối quan hệ giữa dòng điện ID và điện áp UGS. Đồ thị biểu diễn của nó là một đường có dạng gần như đường cong parabol, gọi là đặc tuyến điều khiển hay đặc tuyến truyền đạt. Quan hệ này được thể hiện bằng hàm ID = f(UGS) khi điện áp UDS không đổi. Ta có thể vẽ được đường đặc tuyến truyền đạt này bằng cách suy từ đặc tuyển ra (hình 1.74), hoặc vẽ trực tiếp theo phương trình Shockley.

Qua đường đặc tuyến truyền đạt ta thấy: khi thay đổi điện áp trên cực cổng thì bề dày của lớp tiếp xúc P- N sẽ thay đổi, làm cho tiết diện của kênh cũng thay đổi theo. Do đó điện trở của kênh thay đổi và cường độ dòng điện qua kênh cũng thay đổi. Như vậy điện áp trên cực cổng UGS đã điều khiển được dòng điện ở cực máng ID.

Theo lý thuyết, khi UGS=UD thì bề rộng của kênh giảm xuống 0 và dòng điện máng bão hoà IDSS = 0. Nhưng với linh kiện thực tế thì có một số dòng dò vẫn chảy qua kênh ngay cả khi ở điều kiện ngắt |UGS| > |UP|.

Dòng điện ngược cực cổng lGs là dòng điện chạy từ cực cổng đến cực nguồn khi cực máng chập với cực nguồn trong trường hợp |UGS| > |UP|.

Thông thường dòng lgs bằng khoảng vài nA đối với FET chế tạo bằng Silic.

4. Những mối quan hệ giữa BJT và JFET (hình 1.75)

Xem tiếp về dạng còn lại của FET là MOSFET (Metal Oxide Semiconductor FET) loại FET có cực cửa cách điện là lớp ôxít, theo đường dẫn này

❀◕ ‿ ◕❀